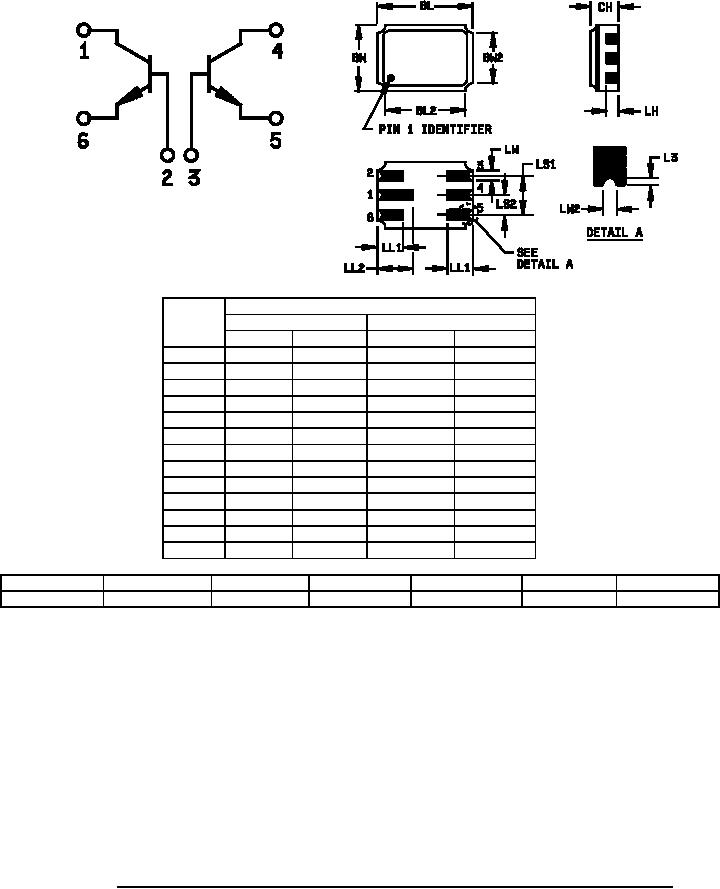

MIL-PRF-19500/317R

U

Dimensions

Ltr.

Inches

Millimeters

Min

Max

Min

Max

BL

.240

.250

6.10

6.35

BL2

.250

6.35

BW

.165

.175

4.19

4.44

BW2

.175

4.44

CH

.066

.080

1.68

2.03

L3

.003

.007

0.08

0.18

LH

.026

.039

0.66

0.99

LL1

.060

.070

1.52

1.78

LL2

.082

.098

2.08

2.49

LS1

.095

.105

2.41

2.67

LS2

.045

.055

1.14

1.39

LW

.022

.028

0.56

0.71

LW2

.006

.022

0.15

0.56

Pin number

1

2

3

4

5

6

Transistor

Collector no. 1

Base no. 1

Base no. 2

Collector no. 2

Emitter no. 2

Emitter no. 1

NOTES:

1. Dimensions are in inches.

2. Millimeters are given for general information only.

3. Dimension CH controls the overall package thickness. When a window lid is used, dimension CH must

increase by a minimum of .010 inch (0.254 mm) and a maximum of .040 inch (1.020 mm).

4. The corner shape (square, notch, radius) may vary at the manufacturer's option, from that shown on the

drawing.

5. Dimensions LW2 minimum and L3 minimum and the appropriate castellation length define an unobstructed

three-dimensional space traversing all of the ceramic layers in which a castellation was designed.

(Castellations are required on the bottom two layers, optional on the top ceramic layer.) Dimension LW2

maximum and L3 maximum define the maximum width and depth of the castellation at any point on its

surface. Measurement of these dimensions may be made prior to solder dipping.

6. The co-planarity deviation of all terminal contact points, as defined by the device seating plane, shall not

exceed .006 inch (0.15mm) for solder dipped leadless chip carriers.

7. In accordance with ASME Y14.5M, diameters are equivalent to φx symbology.

FIGURE 5. Physical dimensions - surface mount (dual transistors, U version only, 2N2369AU, 2N3227U).

8

For Parts Inquires call Parts Hangar, Inc (727) 493-0744

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business